概要

私たちはコンピュータのシステムの理論限界性能と実際に達成できたソフトウェア実行性能との差を分析し、モデル化したり数理最適化技術を駆使し、アプリケーション特化型の高位最適化技術として展開することを研究しています。大規模なプログラムのシステム性能の最適化における生産性向上を目指すツールとして、プログラム実行中に出現する関数やループの正確なネスト構造を動的に検出するpMarker法やキャッシュライン競合シミュレータC2Sim(Cache-line conflict simulator)を開発しました。

従来技術

・性能チューニングや最適化のために、ループ構造を理解する必要があり、多くの労力が必要です。

・発生した競合の数を返すのみで、どこで、なぜ競合が発生しているのかを見つける必要があります。

優位性

・ループネスト構造とその実行時の重みを正確に示し、コード実行特性の理解を支援可能です。

・キャッシュラインの競合が、どこで、なぜ競合が発生したのかを効果的に検出することができ、性能チューニングの半自動化を実現します。

特徴

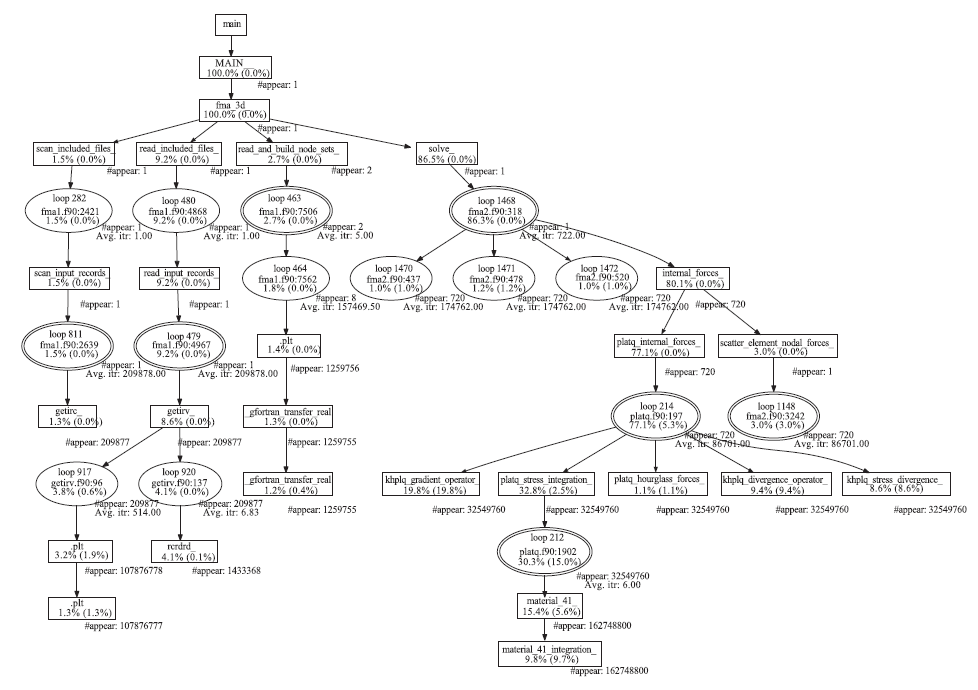

1.pMarker法によるL-CCT(Loop-Call Context Tree)の抽出

- 正確なループ構造をコード実行時にバイナリ計装技術を使って抽出できます。再コンパイル、専用のOS カーネルやライブラリのプレロードといった特殊な実行環境を用意する必要がなく、ソースコードにアクセスすることなく最適化済みの実行コードを解析の入力とできます。

- L-CCT(Loop-Call Context Tree)を使って実際のプログラム実行で現れたループネストと関数呼び出し関係を表現できます。加えて、動的なデータ依存関係も検出し、LCCT+Mグラフとして表示することができます(図1)

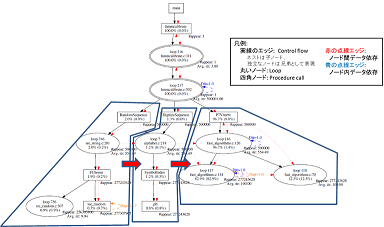

2.C2Simの特徴

- キャッシュライン競合をその発生の正確な検出、原因箇所の特定、及び、チューニング戦略の提示します。

- FA(fully-associative)キャッシュとSA(set-associative)キャッシュを同時にシミュレーションし、競合を検出し、どこでなぜ競合が発生したのかを特定できます。

⇒チューニングするべき箇所を特定して性能向上できることを実証しました。(図2)

実用化イメージ、想定される用途

・大規模なHPC(High Performance Computing:高性能コンピューティング)アプリケーション開発

・大規模な多次元配列を計算する典型的な科学計算アプリケーション

実用化に向けた課題

・pMarker法をLCCTグラフとしての可視化だけではなく、機械学習と組み合わせプログラムの自動最適化/並列化に応用すること

・C2Simを完全自動チューニングシステムの基盤としての拡張、新しいコード変換機構の開発

研究者紹介

佐藤 幸紀 (さとう ゆきのり)

豊橋技術科学大学 情報・知能工学系 准教授

researchmap

研究者からのメッセージ(企業等への提案)

様々な角度から、プログラミング、コンピューティングの技術・科学・アートを探求し、実践していく研究を行っております。この技術にご興味をお持ちの企業の技術相談をお受けします。また共同研究等のご検討の際にはご連絡ください。

知的財産等

掲載日:2021年03月11日

最終更新日:2021年03月11日