山根 啓輔(やまね けいすけ)

| 所属 | 電気・電子情報工学系 |

|---|---|

| 職名 | 准教授 |

| 専門分野 | 半導体工学、結晶工学 |

| 学位 | 博士(工学) 豊橋技術科学大学 |

| 所属学会 | 応用物理学会 |

| yamane@ee ※アドレスの末尾に「.tut.ac.jp」を補完してください |

|

| 研究室web | http://www.int.ee.tut.ac.jp/oeg/ |

| 研究者情報(researchmap) | 研究者情報 |

研究紹介

情報技術や高度センシング技術によって生み出された膨大な情報は我々の生活を確実に豊かにしてきました。シリコン集積回路はこれらの情報を処理・活用するキーデバイスとして重要な役割を担っています。そのシリコン集積回路は、電気信号のみによる時系列・直列演算システムを基本としており、物理的制約からこれ以上の飛躍的な性能向上が見込めない段階にあります。本研究では、新しいアプローチとしてシリコン集積回路内に微小受・発光素子を組み込んだモノリシック光電子融合システムを提案しています。将来的にチップ内・チップ間において光通信技術を自在に導入することができれば、超並列・多層演算システムによる高速演算処理や新規計測システムの提案など、集積回路の性能・機能の飛躍的な向上につながると考えられます。

テーマ1:シリコン/III-V窒化物半導体ヘテロ構造を用いたモノリシック光電子融合デバイスの研究開発

概要

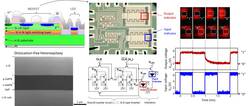

本研究では、Si集積回路作製工程との整合性、発光素子の効率・信頼性の観点から、理想とされるモノリシック光電子融合システムを目標としています。図は、我々が提案しているモノリシック光電子融合システムのプロトタイプです[1]。結晶成長技術を駆使してSi基板上にIII-V-N発光層およびSi集積回路層を無欠陥で作製する技術を確立しました[2](図左)。さらに、本学のLSI工場を利用してビットカウンタ回路(図中央)を作製し、発光素子と集積回路がワンチップ上で動作可能であることを世界で初めて実証しています(図右)。今後、発光効率の向上、受光素子の集積化を実現し、超並列演算機能を持たせた回路の作製を目指します。

[1] K. Yamane, K. Noguchi, S. Tanaka, Y. Furukawa, H. Okada, H. Yonezu, A. Wakahara, “Operation of monolithically-integrated digital circuits with light emitting diodes in lattice-matched Si/III-V-N/Si heterostructure”, Applied Physics Express 3 (2010) 074201.

[2] K. Yamane, T. Kawai, Y. Furukawa, H. Okada, A. Wakahara, “Growth of low defect density GaP layers on Si substrates within the critical thickness by optimized shutter sequence and post growth annealing” , Journal of Crystal Growth 312 (2010) 2179.

担当授業科目名(科目コード)

電気・電子情報工学実験II